2021. 7. 24. 08:50ㆍ개발/컴퓨터구조

이전에 클럭을 통해서 컴퓨터에게 현재와 과거의 개념을 부여했다면, 이번에는 어떻게 컴퓨터가 과거의 bit값을 기억하는지 알아본다.

비트를 기억하는 방법은 크게 래치(Latch)와 플립플롭(Flip-Flop)이 있는데 오늘은 래치에 대해서 작성한다.

Latch

NOT, AND, OR 게이트를 이용해서 가장 기본적인 형태의 래치를 만들어본다.

입력은 set과 reset이 있으며, OR 게이트의 결과인 out이 AND의 입력으로 사용되었다. 이런 식의 연결을 되먹임(feedback)이라고 한다.

set과 reset을 입력했을때 out의 결과가 어떻게 변하는지 살펴본다.

예시에 대한 결과를 정리해보면 아래와 같다.

- reset이 1인 경우 out은 set의 값으로 셋팅되게 된다. ( Why? AND게이트의 결과가 항상 0이기 때문이다. )

- reset이 0이면서 set이 1이면 set의 값이 out으로 결정된다. ( Why? OR 게이트에선 어느 한쪽의 입력이 1이면 결과는 무조건 1이 나오기 때문이다. )

- reset이 0이면서 set이 0이면 이전의 out값이 그대로 out으로 출력된다. 이 경우, 이전값을 기억하게 된다!!

위 회로를 보면 reset의 입력이 0일때 되먹임이 초기화 되는 작업이 수행된다.

이를 액티브 로우(Active Low)라고 한다. 어떤 작업을 수행하려고 할때 1(High)이 아닌 0(Low)을 입력함으로써 작업을 시작할 수 있도록 하는것을 뜻한다. 반대는 액티브 하이(Active High).

S-R latch

이제 좀 더 그럴듯한 래치를 만들어보자. 흔히 알고 있는 S-R 래치이다. 예상했겠지만 이름에 있는 S는 Set, R은 Reset을 의미한다. 현재 읽고 있는 컴퓨터구조론 책에 따르면 NOR 게이트 S-R 래치보다 NAND 게이트 S-R래치가 효율(전력이나 생성 복잡도)측면에서 더 좋다고 한다.

입력이 2개인 NAND 게이트의 특성.

- 입력 중에 0이 하나라도 있으면 결과는 1이 나온다.

- 입력이 1이면 다른 입력에 따라 결과가 달라진다.

S-R래치를 보면 NAND 게이트 2개와 S,R을 액티브 로우로 입력하는 모습이다. 각 NAND 게이트의 출력은 반대쪽 NAND의 입력으로 사용된다. S-R 래치는 보수 출력을 가진다. (Q와 Q-bar) 즉, 한쪽의 출력이 1이면 다른쪽 출력은 0이 나와야한다. ( 아래 그림부터 set, reset의 입력과 NOT 게이트를 하나로 합쳐서 set-bar로 바로 표기한다. )

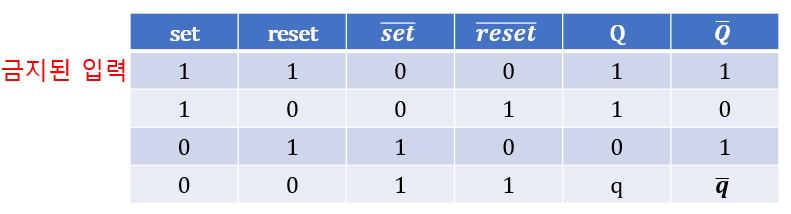

S-R래치의 특성표는 아래와 같다. set과 reset이 모두 1로 입력되는 경우는 출력 Q의 보수 관계가 깨지기 때문에 입력자체가 금지된다.

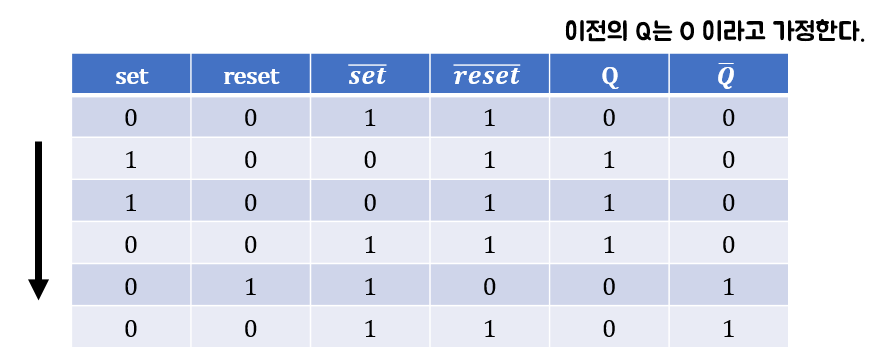

구체적인 예시를 하나 살펴보자. 앞서 말한대로 NAND 게이트의 입력 중 0이 하나라도 있으면 결과는 1이 나온다.만 기억하고 있으면 이해하기가 좀더 수월하다.

set과 reset의 입력이 0일때 (set-bar=1, reset-bar=1) 현재 출력은 이전의 출력과 동일하게된다. 즉, 이전의 값을 기억한다.

S-R 래치 뿐만아니라 순차회로를 학습하다보면 위 처럼 이전 입력을 가정해서 예시를 만들어야하는 경우가 많다. 그런데 컴퓨터 전원을 켜고 최초의 클럭이 S-R 래치에 들어왔을때는 이전 상태가 없는데 어떻게 되는걸까 하는 의문이 든다. 실제로 S-R래치가 최초 수행될때 이전값은 "알수없음" 상태이다. ( 심지어 외부의 온도나 습도에 따라 전원을 켤때마다 최초값이 달라지는 경우가 있다고한다. ) 따라서 순차회로의 초기값을 셋팅해주는 별도의 작업을 수행해줘야 한다.

SR Latch (Flip Flop) beginning Inputs?

Ok this is probably a basic question, but I understand how SR latches work except one thing. In the R input and S input you can make them 0 or 1.....but what about the input lines next to them (That

electronics.stackexchange.com

Gate S-R latch

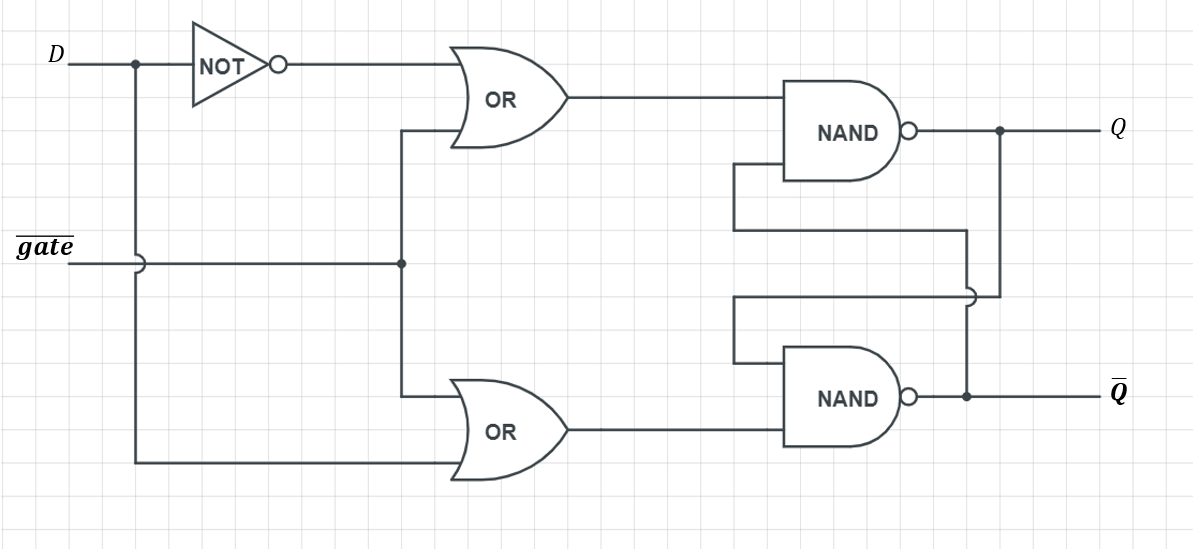

특정 타이밍에 S-R래치를 동작시키기 위한 기능을 추가해보자. 위에서 만든 S-R 래치로는 set과 reset의 입력을 무시할 수 있는 방법이 없다. 하지만 S-R 래치에서 OR 게이트를 추가함으로써 원하는 기능을 구현할 수 있다. S-R 래치를 동작을 On/Off 하기위해 gate입력을 사용한다.

gate-bar가 1이면 OR 게이트의 특성상 출력은 항상 1일수 밖에 없다. 따라서 set과 reset의 값에 상관없이 NAND 게이트에는 1이 입력으로 들어간다. 위 S-R Latch에서도 봤듯이 set-bar와 reset-bar의 입력이 모두 1이면 이전값을 보존하게된다.

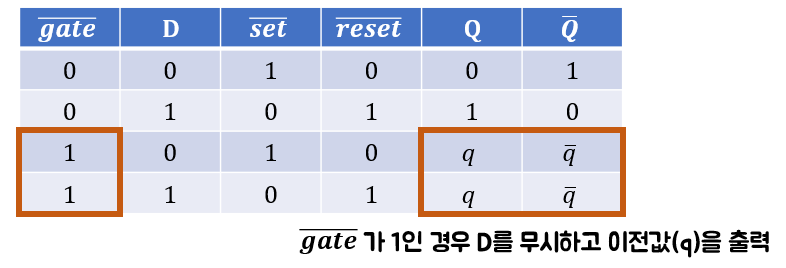

Gate-D latch

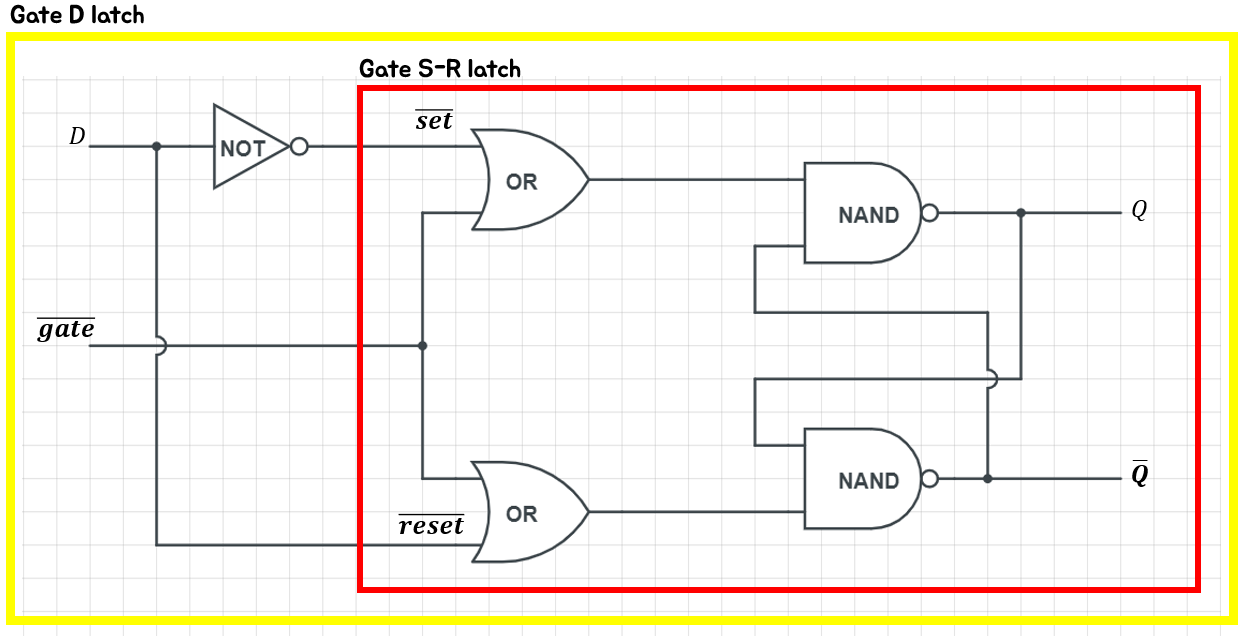

set, reset 대신 하나의 입력으로 래치를 구현할 수도 있다. 위의 Gated S-R래치를 응용해 Gate-D latch를 구현한다.

Gate-D latch를 뜯어보면 Gate S-R latch에서 set과 reset의 입력을 D하나로 묶은것 밖에 없다.

이전의 Gate S-R latch에선 set, reset 신호를 각각 입력해야했지만 Gate-D latch에선 D만 입력해주면 자연스럽게 set과 reset이 OR게이트에 각각 입력되게 된다. Gate-D latch의 특성은 set과 reset은 서로 보수관계의 입력만 가능하다는 것이다. ( Why? D를 두개로 나눠서 입력하게 되는데 그중 하나는 NOT 게이트를 지나가야한다. )

진리표를 그려보면 S-R 래치보다 효율적임을 알 수 있다. 입력은 gate와 D로 간소화 시켰으며, 자연스럽게 set과 reset의 금지입력(set=1, reset=1)을 막을 수 있다!

참고자료

Online circuit simulator & schematic editor - CircuitLab

Powerful online circuit simulator and schematic editor. Easy to learn.

www.circuitlab.com

'개발 > 컴퓨터구조' 카테고리의 다른 글

| [순차회로] 플립플롭 (0) | 2021.07.25 |

|---|---|

| 클럭(Clock) (0) | 2021.07.18 |

| 스위치부터 집적회로까지 (0) | 2021.07.17 |